首先,说说中断优先级,所有中断均有一个优先级,

1、 更低的优先级数字代表着更高优先级

2、 除了RESET, Hard fault, NMI等系统级中断,其他所有中断优先级均可配置为”0~31″。

如果软件没有配置这些中断的优先级,那么所有中断的优先级默认为最高优先级”0″。此处 实例说明这个中断优先级的概念,假设三个外部中断”A,B,C”,”A,B”配置为”0″,”C”配置为”1″,

1、 如果三个中断同时产生,那么”A,B”中断优先”C”中断运行。

2、 “A,B”中断同时产生,谁更优先执行呢?那就根据中断向量表的排号,低的优先执行。

3、 若是”C”的中断正在运行,此时”A”的中断发生,那么”A”的中断会抢占”C”的执行权限,优先执行。

4、 若是”A”的中断正在运行,此时”B”的中断发生,那么新产生的”B”中断会进入等待状态,等 待”A”执行完毕再执行。

以上,只是单纯的判断优先级值来控制中断的顺序,为了增强中断的控制逻辑,ARM新增了优先级 组的概念。即相同的优先级等级可以分配在一组优先级内,在这一组优先级内再来定义次优先级,具 体是怎么一个概念呢?还是假设有四个中断”A,B,C,D”,”A,B,C”配置在优先级组”0″内,”A,B”中断配 置次优先级”0″,”C”配置为次优先级”1″,”D”则配置为优先级组”1″

1、 若”A,D”中断同时产生,则优先级高的”A”会优于”D”中断执行。

2、 若”A,C”中断同时产生,则优先级次优先级高的”A”会优先执行。

3、 若”A,B”中断同时产生,则根据中断向量表的位置,排号低的优先执行。

4、 若”D”正在执行中断,此时”A”中断来了,那么”A”中断会抢占”D”中断优先执行。因为”A”所 在的优先级组高于”D”。

5、 若”C”正在执行中断,此时”A”中断来了,那么”A”中断会等待”C”执行完毕再执行。因为属于同一优先级组。

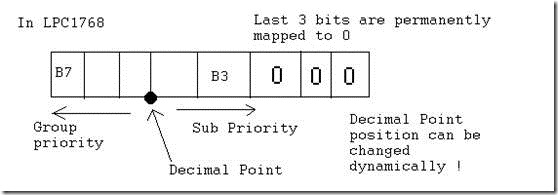

ARM用了一个8位寄存器来定义优先级组和次优先级的概念。中间可以选择一个端点,高位表示有多少个主优先级,低位表示有多少个次优先级。而LPC1769只用了其中5位。

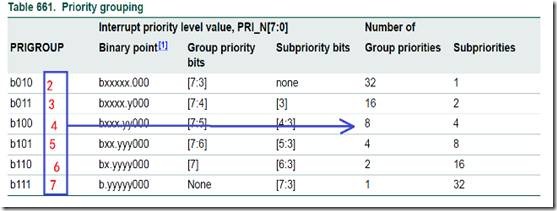

CM3每个中断都有一个优先级寄存器,对LPC1768来说,使用了高5位,低3位固定为0。

在CM3权威指南中

因为LPC1768低3位固定为0,所以优先级分组是从2-7.

最好选择分组2,B7-B3表达抢占优先级,没有子优先级位段。总共可以设置0-31个抢占优先级中断。抢占优先级可以实现中断嵌套。